# Lecture Notes in Computer Science

3471

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Babak Falsafi T.N. Vijaykumar (Eds.)

# Power-Aware Computer Systems

4th International Workshop, PACS 2004 Portland, OR, USA, December 5, 2004 Revised Selected Papers

#### Volume Editors

Babak Falsafi

Carnegie Mellon University

Electrical and Computer Engineering Dept.

A305 Hamerschlag Hall, 5000 Forbes Avenue, Pittsburgh, PA 15213, USA

E-mail: babak@cmu.edu

T.N. Vijaykumar

Purdue University

School of Electrical and Computer Engineering

Department of Computer Science

ECE/EE 465 Northwestern Avenue, West Lafayette, Indiana 47907-1285, USA

E-mail: vijay@ecn.purdue.edu

Library of Congress Control Number: 2005936777

CR Subject Classification (1998): B.7, B.8, C.1, C.2, C.3, C.4, D.4

ISSN 0302-9743

ISBN-10 3-540-29790-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-29790-1 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper SPIN: 11574859 06/3142 5 4 3 2 1 0

## **Preface**

Welcome to the proceedings of the Power-Aware Computer Systems (PACS 2004) workshop held in conjunction with the 37th Annual International Symposium on Microarchitecture (MICRO-37). The continued increase of power and energy dissipation in computer systems has resulted in higher cost, lower reliability, and reduced battery life in portable systems. Consequently, power and energy have become first-class constraints at all layers of modern computer systems. PACS 2004 is the fourth workshop in its series to explore techniques to reduce power and energy at all levels of computer systems and brings together academic and industry researchers.

The papers in these proceedings span a wide spectrum of areas in power-aware systems. We have grouped the papers into the following categories: (1) microarchitecture- and circuit-level techniques, (2) power-aware memory and interconnect systems, and (3) frequency- and voltage-scaling techniques.

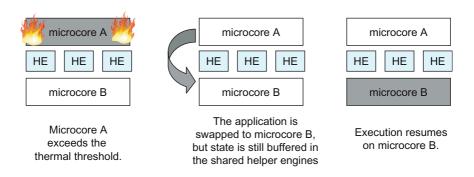

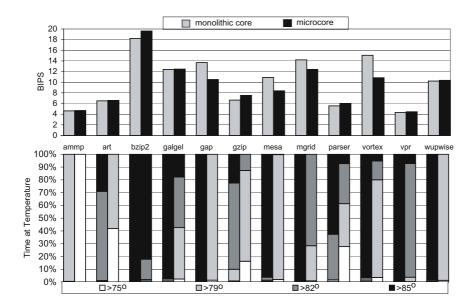

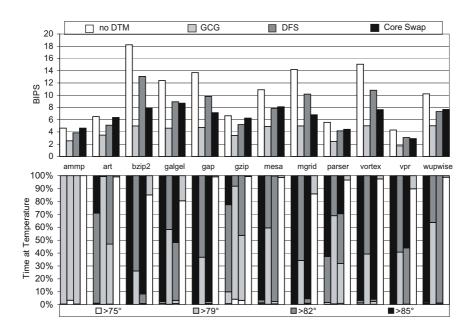

The first paper in the microarchitecture group proposes banking and write-back filtering to reduce register file power. The second paper in this group optimizes both delay and power of the issue queue by packing two instructions in each issue queue entry and by memorizing upper-order bits of the wake-up tag. The third paper proposes bit slicing the datapath to exploit narrow width operations, and the last paper proposes to migrate application threads from one core to another in a multi-core chip to address thermal problems.

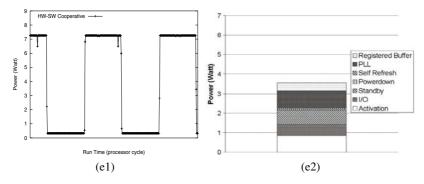

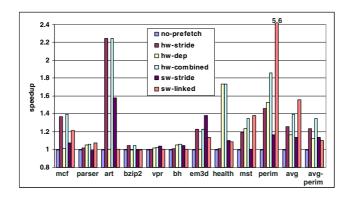

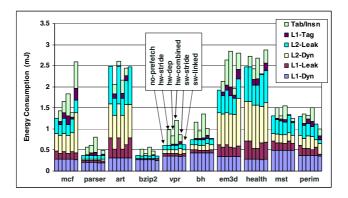

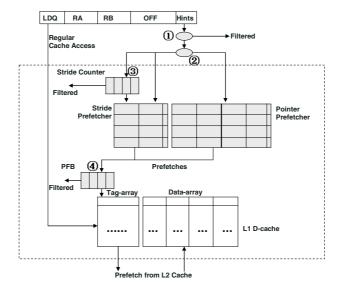

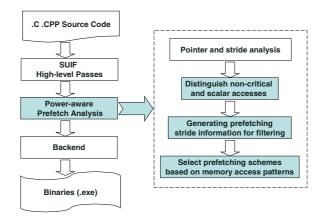

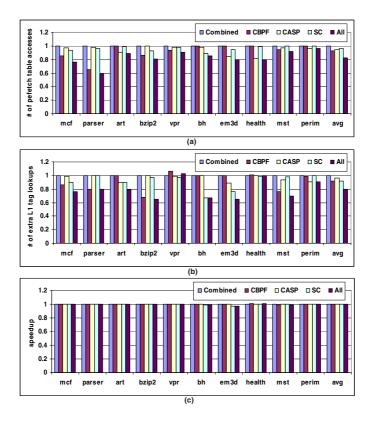

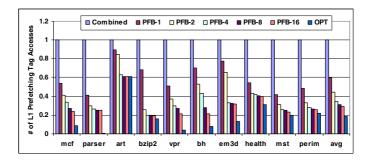

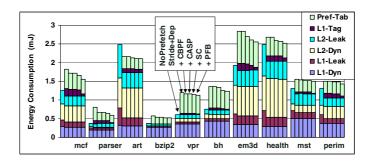

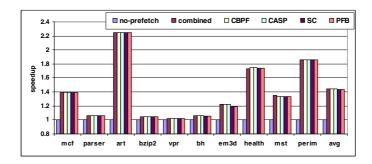

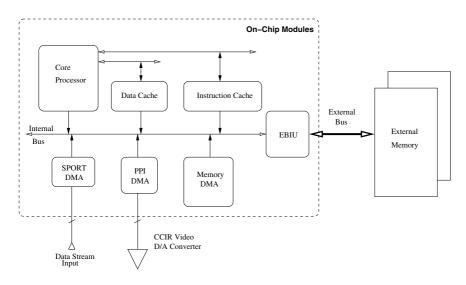

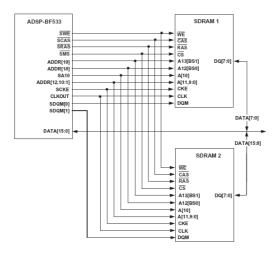

The second group of papers on power-aware memory and interconnects starts with a contribution which proposes hardware—software co-operation to reduce main memory power dissipation. The paper suggests combining process-level information from the software and DRAM-bank-level information from the hardware for significant power reduction. The second paper in this group uses compiler-assist to make hardware prefetching more energy efficient by filtering out unnecessary and ineffective prefetching. The third paper explores modeling of external bus power dissipation and evaluation of coding techniques for bus power reduction. The last paper proposes context-independent coding for reducing power in off-chip interconnects to avoid the disadvantage of context-dependent coding not being applicable to commodity memories because of requiring collaboration between the memory controller and SDRAM.

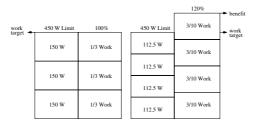

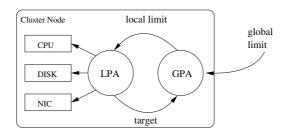

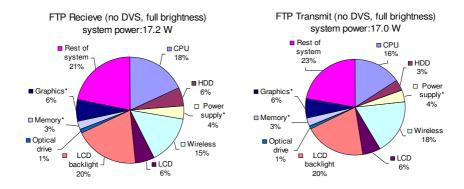

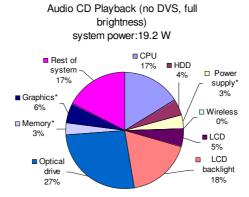

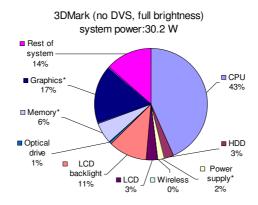

The last group proposes frequency- and voltage-scaling techniques. The first paper in this group recommends throttling processor clock speed during low-utilization phases. The second paper scales the processor voltage according to the CPU-boundedness of the application. The third paper investigates the potential of hardware overprovisioning to increase throughput in data centers while remaining within a power budget. The last paper shows a detailed breakdown of power consumption in the various components of a modern laptop.

## VI Preface

The success of PACS 2004 has been due to the high quality of the submissions, the efforts of the Program Committee, and the attendees. We would like to thank Vivek De for his informative keynote address, which described design challenges and opportunities for power-limited microprocessors. We would also like to thank Jose Gonzalez, Glen Reinman, Srikanth Srinivasan and other members of the MICRO-37 Organizing Committee who helped arrange the local accommodation and publicize the workshop.

December 2004

Babak Falsafi T. N. Vijaykumar

## PACS 2004 Program Committee

Babak Falsafi, Carnegie Mellon University (Co-chair) T. N. Vijaykumar, Purdue University (Co-chair)

David Albonesi, Cornell University Csaba Andras Mortiz, University of Massuchusetts Krste Asanovic, Massachusetts Institute of Technology Luca Benini, Universitá di Bologna Frederic Chong, University of California, Davis Kanad Ghose, State University of New York, Binghamton Christoforos Kozyrakis, Stanford University Uli Kremer, Rutgers University Charles Lefurgy, IBM, Austin Research Lab Yung-Hsiang Lu, Purdue University Avi Mendelson, Intel, Israel Microarchitecture Lab Andreas Moshovos, University of Toronto Daniel Mosse, University of Pittsburgh Vijaykrishnan Narayanan, Pennsylvania State University Li-Shiuan Peh, Princeton University Parthasarathy Ranganathan, HP Labs Eric Rotenberg, North Carolina State University Mircea Stan, University of Virginia Se-Hyun Yang, Samsung

# **Table of Contents**

| Microarchitecture- and Circuit-Level Techniques                                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An Optimized Front-End Physical Register File with Banking and Writeback Filtering                                                                                       |     |

| Miquel Pericàs, Ruben Gonzalez, Adrian Cristal, Alex Veidenbaum, Mateo Valero                                                                                            | 1   |

| Reducing Delay and Power Consumption of the Wakeup Logic Through<br>Instruction Packing and Tag Memoization<br>Joseph Sharkey, Dmitry Ponomarev, Kanad Ghose, Oguz Ergin | 15  |

| Bit-Sliced Datapath for Energy-Efficient High Performance Microprocessors                                                                                                |     |

| Sumeet Kumar, Prateek Pujara, Aneesh Aggarwal                                                                                                                            | 30  |

| Low-Overhead Core Swapping for Thermal Management  Eren Kursun, Glenn Reinman, Suleyman Sair, Anahita Shayesteh,  Tim Sherwood                                           | 46  |

| Power-Aware Memory and Interconnect Systems                                                                                                                              |     |

| Software-Hardware Cooperative Power Management for Main Memory H. Huang, K.G. Shin, C. Lefurgy, K. Rajamani, T. Keller, E. Hensbergen, F. Rawson                         | 61  |

| Energy-Aware Data Prefetching for General-Purpose Programs  Yao Guo, Saurabh Chheda, Israel Koren, C. Mani Krishna,  Csaba Andras Moritz                                 | 78  |

| Bus Power Estimation and Power-Efficient Bus Arbitration for System-on-a-Chip Embedded Systems  Ke Ning, David Kaeli                                                     | 95  |

| Context-Independent Codes for Off-Chip Interconnects  Kartik Mohanram, Scott Rixner                                                                                      | 107 |

| Frequency-/Voltage-Scaling Techniques                                                                                                                                    |     |

| Dynamic Processor Throttling for Power Efficient Computations  Masaaki Kondo, Hiroshi Nakamura                                                                           | 120 |

## X Table of Contents

| Effective Dynamic Voltage Scaling Through CPU-Boundedness                      |     |

|--------------------------------------------------------------------------------|-----|

| Detection                                                                      |     |

| Chung-Hsing Hsu, Wu-Chun Feng                                                  | 135 |

| Safe Overprovisioning: Using Power Limits to Increase Aggregate<br>Throughput  |     |

| Mark E. Femal, Vincent W. Freeh                                                | 150 |

| Power Consumption Breakdown on a Modern Laptop  Aqeel Mahesri, Vibhore Vardhan | 165 |

| Author Index                                                                   | 181 |

# An Optimized Front-End Physical Register File with Banking and Writeback Filtering

Miquel Pericàs<sup>1,3</sup>, Ruben Gonzalez<sup>1</sup>, Adrian Cristal<sup>1</sup>, Alex Veidenbaum<sup>2</sup>, and Mateo Valero<sup>1,3</sup>

<sup>1</sup> Computer Architecture Department, Technical University of Catalonia (UPC)

<sup>2</sup> Information and Computer Science, University of California at Irvine (UCI)

<sup>3</sup> Barcelona Supercomputing Center (BSC)

{mpericas, gonzalez, adrian, mateo}@ac.upc.edu,

alexv@matrix.ics.uci.edu

**Abstract.** Register file design is one of the critical issues facing designers of out—of—order processors. Scaling up its size and number of ports with issue width and instruction window size is difficult in terms of both performance and power consumption. Two types of register file architectures have been proposed in the past: a future logical file and a centralized physical file.

The centralized register file does not scale well but allows fast branch misprediction recovery. The Future File scales well, but requires reservation stations and has slow misprediction recovery. This paper proposes a register file architecture that combines the best features of both approaches. The new register file has the large size of the centralized file and its ability to quickly recover from branch misprediction. It has the advantage of the future file in that it is accessed in the "front end" allowing about 1/3rd of the source operands that are ready when an instruction enters the window to be read immediately. The remaining operands come from bypass logic / instruction queues and do not require register file access. The new architecture does require reservation stations for operand storage and it investigates two approaches in terms of power–efficiency.

Another advantage of the new architecture is that banking is much easier to use in this case as compared to the centralized register file. Banking further improves the scalability of the new architecture. A technique for early release of short–lived registers called *writeback filtering* is used in combination with banking to further improve the new architecture. The use of a large front–end register file results in significant power savings and a slight IPC degradation (less than 1%). Overall, the resulting energy–delay product is lower than in previous proposals.

## 1 Introduction

Memory-based structures in the core of modern microprocessors have increasing energy requirements as frequencies grow. One such structure is the register file. Its size and the number of read/write ports required increases with issue width making it difficult to implement at high clock frequencies.

Two main approaches to register file design were used in the past, neither of which solved the above-mentioned problems. One approach was an architecture based on the Future file, which has a logical register file updated in commit and the future register

file in the "front-end" holding the most recent, uncommitted value for each logical register. The advantages of the future file are that it is not very large, has no renaming, can be read in the front-end and is not written if a more recent instruction assigning it is in the window. The disadvantages are that on branch mis-prediction, intermediate register values need to be recovered (typically after the mis-predicted branch commits), it needs reservation stations in the back-end, and its size cannot be increased. The mis-prediction recovery can lead to a significant IPC loss, especially given increasing memory latencies.

An alternative approach is a single, large physical register file, without a separate architectural register file. It is typically accessed after an instruction is scheduled to execute, even if source operand values were available when the instruction entered the window. This is the approach in the MIPS R10000 [1] and many later processors. Its advantages are increased size and fast mis–prediction recovery. Disadvantages are more complex renaming and longer value lifetime in the file due to lack of logical register file. Overall, it needs to be both large and heavily multi–ported, making it difficult to implement and increases its energy consumption significantly.

The new architecture proposed in this paper combines the best features of the two above—mentioned approaches: arbitrary size and fast mis—prediction recovery of the physical register file; and placement in the front—end, early operand read, and potential lack of write—back of the future file. It can be thought of as a physical register file moved to the front end and accessed after renaming. This allows a large fraction of operands to be accessed as an instruction enters the window, which is now the only read access to the register file. These values are stored in "reservation stations" integrated into the instruction queue, which can also be thought of as a replicated portion of the register file. A value coming from writeback may be written to this file if there are instructions waiting for it. Finally, many registers hold values for mis—prediction recovery, some of which can be released if they cannot affect recovery.

The approach proposed here uses a single register file containing all physical registers, the Front-end Physical Register File (FPRF). Thus restarting execution after a mispredicted branch can be done using a rename map recovery from check-points made on conditional branches.

As source operand registers are renamed, it can be determined if a register value has already been computed. The FPRF is read only in this case, significantly reducing its access frequency. Combined with the higher IPC due to faster branch recovery, it has a better energy-delay product compared to the two traditional approaches.

A new structure to hold such "early read" values is created in the instruction queue payload RAM. Its function is similar to that of reservation stations. It is smaller than the physical register file and thus consumes less energy. It is written into by completing instructions, if the produced value is a source operand of a waiting instruction.

This paper also investigate the use of banking in the FPRF architecture. Due to lower access frequency of the FPRF this is much easier to do than in a standard centralized physical register file Finally, writeback filtering, a technique to eliminate unnecessary writebacks into the register file is investigated and shown to be quite effective.

## 2 Related Work

The body of related work on register file energy optimization is large. Many recent papers have proposed mechanisms to reduce the number of the ports by means of modifying the register file architecture, such as [4] [5] [6] [7]. A reduced number of ports may be more efficient both in terms of energy and access time, which can improve performance.

A different approach is to reorganize the registers into several files, concentrating most activity on small files with low power consumption. [8] is an example of this approach based on the isolation of narrow operands. Hierarchical register files, such as those presented in [9] [10] [11] and clustering techniques such as [12] [5] are another example of this technique, which effectively trades size, speed and power consumption.

Another research direction has focused on changing the register allocation algorithm to reduce the register requirements of the architecture. *Early Release* frees registers before the commit stage of the next instruction that writes to the same logical registers [13] [14] [15]. *Virtual registers* [16] try to delay the allocation of the physical register until the writeback stage of the instruction. Another approach to reduce registers is to exploit repeated values in the registers [17] [18].

Our approach is somewhat based on the *Future File* organization which was proposed in 1984 [19]. In the original proposal, operands are provided to instructions via a logical register file in the front-end which received the name of *Future File*. The main difference with our architecture is that we are basing our design around the concept of physical registers to identify the state of the processor. Thus, while a Future File architecture can only recover from a mispredicted branch by draining the ROB, our proposed architecture can recover directly from the physical registers. Future File architectures are still being used in the form of the AMD K7 and K8 microarchitectures [20].

The future file can be extended with rename buffers to provide access to the full processor state at once. This has been implemented in the PPC620 [3] and POWER3 processors. However, these two processors still require the architectural state to be copied from the rename buffers during retirement. Having an architectural register file in the front-end shortens the pipeline one stage (access can be performed in parallel to rename stage) but increases the number of on-chip register transfers.

Research by Tseng et al. on banked register files [21] proposed an efficient implementation of banking for the register file of a MIPS R10000-like architecture. In the following sections is will be compared to the architecture proposed in this paper.

Finally, the *Writeback Filtering* technique, based on the release of short-lived values, is described in [22] and, in the context of VLIW architectures, in [23]. However, as will be shown here, the specific architectecture presented here allows to support *Writeback Filtering* in innovative ways.

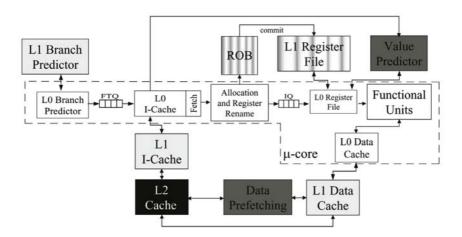

## 3 Front-End Physical Register File

This section describes the *Front-End Physical Register File Architecture* (FPRF). The FPRF pipeline provides instructions with their operands as soon as the operands are available. Further, it implements a central physical register file in the front-end that

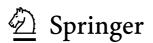

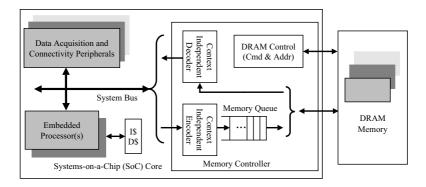

Fig. 1. The Front-End Physical Register File Architecture

allows for fast recovery with little complexity. It also allows to apply banking with high efficiency.

The FPRF Architecture, like a Future File, reads available registers in the front end. However, in this approach the registers are accessed via a mapping into a centralized register file that contains all registers. This has two implications:

- Access to computed values in the front-end needs to be delayed until the rename stage has completed.

- 2. The number of registers in the front-end, being equal to the total number of registers, is much larger than it is in a Future File Architecture.

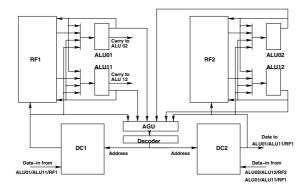

Figure 1 shows the FPRF architecture. Instructions, after going through the decode stage, enter the rename stage where source and destination registers are mapped to physical registers. Using this information an instruction may access the FPRF, a two stage process consisting of arbitration and data access. After available values have been given to the instruction, it is inserted into the corresponding instruction queue.

The back-end pipeline works as follows: When a functional units generates a result, the register tag is sent to all instructions in the queue. If there is an instruction waiting for it, the value is written into the corresponding entry of the Value Register File (VRF), which is part of the payload RAM of the instruction queue. The VRF is driven by the wakeup logic signals and can be implemented as a register file that does not require a decode stage. The value also gets written into the FPRF, as indicated by its physical register designator. There is also a possibility that a value is bypassed to a dependent instruction.

## 3.1 FPRF Pipeline

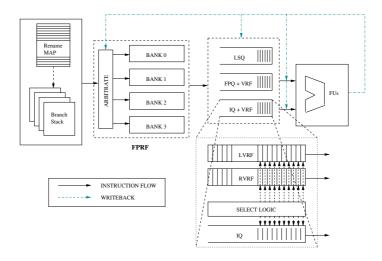

The pipeline of the FPRF Microarchitecture is shown in Fig. 2. It adds one stage to a commonly used 8-stage pipeline consisting of: fetch, decode, rename, queue, issue,

Fig. 2. The Pipeline of the FPRF Architecture

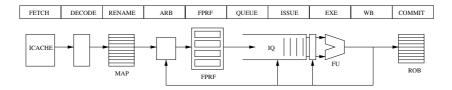

Fig. 3. Source of Integer Operands

operand read, execute, writeback and commit. To support FPRF access in the front-end, two stages are added to the pipeline: arbitration and FPRF Read. In the back-end the operand read stage disappears. This reduces the length to a single additional stage.

In the first new stage the source registers are analyzed to check for bank conflicts in the FPRF access. Conflicts stall all prior stages.

During rename, it is checked if the source registers have computed values. This is implemented via a bit vector with as many entries as logical registers. In the case of the Alpha ISA, modeled here, this requires maintaining two 32-bit vectors, one for the integer and another for the floating point registers. Each entry of this bit-vector indicates whether the corresponding logical register has a computed value. In case the computed value is available a read to the corresponding FPRF register is started.

During the arbitration cycle, priority is given to "older" instructions to access the operands. This makes sure that the front-end does not dispatch instructions to the instruction queues out-of-order.

The number of read ports for each bank has to be at least two, because some instructions must obtain both operands from the same FPRF bank.

Once arbitration has been performed the FPRF read occurs. After the instruction has read the available values it is inserted in the instruction queues. This happens during the *Queue* stage. At the same time, the register values are inserted into the VRF.

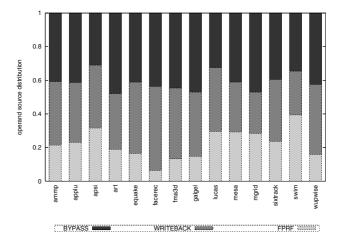

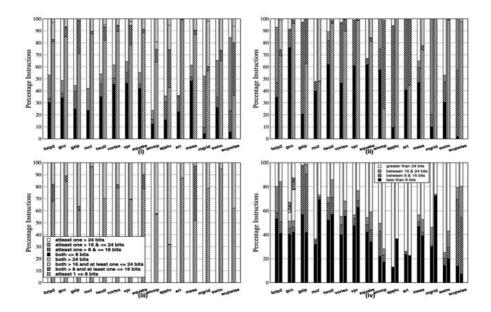

It is clear that the access rate to the FPRF is lower than to the centralized backend physical register file. Lower access rate means that less conflicts will occur in the front-end and also that it will consume less energy. It was observed that the number of integer operands that are obtained from the FPRF is about 40% of the total while for floating point operands this number decreases to around 20%. Figures 3 and 4 show the distribution of integer and fp operand sources averaged over 100 million instructions for each Spec2000 benchmark. The boxes labeled *FPRF* account for operands that were read from the FPRF. The boxes labeled *WRITEBACK* are for operands that were written directly into the VRF from the writeback stage. Finally, the label *BYPASS* refers to those values that are sourced from the bypass network.

Fig. 4. Source of FP Operands

In the event of a branch misprediction the FPRF architecture behaves exactly like the MIPS R10000. First, the processor immediately aborts all instructions fetched along the mispredicted path. Next it restores the register mapping from the branch stack and finally, it starts fetching instructions from the correct path.

## 3.2 Read Sharing

Accesses to the same logical registers are often clustered during program execution. For example, many instructions use the same logical register for both register sources (eg ADD R2, R2, Rd). On the other hand it is also fairly common that the same register is sourced by several instructions without being written to. Such register accesses have a high probability of bank conflict. This suggests that conflicts in the access to the FPRF can be effectively reduced by using the technique known as read sharing [10]. Read sharing allows multiple reads of a same register to happen using a single local port which is connected to several global ports. Previous work on banked register files by Tseng et al. [21] has also used this approach. Read sharing will be evaluated later in the context of the FPRF architecture.

## 3.3 Writeback Filtering

In the FPRF implementation described so far all values are written back to the FPRF during the writeback stage. The front-end of the FPRF needs only to maintain copies for those physical registers that may be needed in the future. This includes all currently mapped registers and all registers that may be needed in the case of a misspeculation or exception recovery. The total number of registers that are generated by writeback is larger than these two numbers combined. Many registers that are renamed twice in a short interval do not appear in any of the mappings. Their storage will not be needed after the consumer reads the value. If this can be detected in time, then the writeback can be filtered and the write to the FPRF can be eliminated. To implement this strategy the processor needs to analyze the mapped registers in all rename checkpoints plus the current mapping and decide if the register that is being written back belongs to the processor state. Checkpoints need to be taken at all instructions that may cause a replay. There are many such instructions but the vast majority are conditional branches and loads. Registers that are not referenced anywhere are candidates to be filtered out during writeback.

One very interesting property of the writeback filtering concept is that lazy implementations can be built that are out of the critical path. The information whether an operand needs to be written back or not can be computed right after the rename stage. However, the operand itself will not be produced until the execution stage has completed, which is at least 5 cycles in the future. In general we can delay the computation of the filter mask a number of cycles equivalent to the distance between rename and writeback. However it has to be noted that delaying this computation will allow many unnecessary writebacks to happen because a physical register that is no longer necessary may appear as mapped in the filter mask even though it does not belong anymore to the current mapping.

This lazy writeback scheme allows the designer to propose slower but pipelined hardware structures to compute the filtering mask. For example, one proposal would be to use a slow multistage OR structure to compute the OR of the several checkpointed rename maps, assuming that a CAM-style renamer is being used. We expect such a structure to be slower, but also less power-hungry compared to precise proposals based on counters such as [13].

Section 5 presents performance results on writeback filtering for a scheme that computes the filter mask immediately. The lazy scheme has not been evaluated but it is expected to have similar performance.

## 4 Experimental Setup

For the evaluation of the FPRF architecture a heavily modified execution driven simulator based on SimpleScalar was used. The simulator executes binaries compiled for the Alpha ISA. Our benchmark suite consists of all benchmarks of the Spec2000 suite compiled with Digital cc using "-O2". We run the benchmark for 100 million of committed instructions.

First a baseline out-of-order microarchitecture with a centralized back-end RF was simulated and then extended using the enhancements proposed in this paper. Finally,

| Fetch/Issue/Commit Width      | 4 instructions/cycle               |

|-------------------------------|------------------------------------|

| Branch Predictor              | Combined bimodal + 2-level         |

| I-L1 size                     | 32 KB, 4-way, 1 cycle latency      |

| D-L1 size                     | 32 KB, 4-way, 2 rd/wr ports, 2 cy- |

|                               | cle latency                        |

| D-L2 size                     | 256 KB, 4-way, 2 rd/wr ports, 10   |

|                               | cycle latency                      |

| Memory Width / Latency        | 32 bytes / 100 cycles              |

| Ports to the Register File    | 8 Read & 4 Write                   |

| Reorder Buffer Size           | 128                                |

| Integer/FP Physical Registers | 160 / 160                          |

| Load/Store Queue              | 128 entries                        |

| Integer/FP Queue              | 32 entries / 32 entries            |

| Integer/FP Functional Units   | 4 (latency 1) / 4 (latency 2)      |

Table 1. Common parameters for all configurations

we implemented the model described in [21] for comparison. The common parameters of all configurations are shown in Table 1.

To evaluate the proposal with the read sharing technique, the 6 configurations summarized in Table 2 and described below were simulated.

- 1. Base-SHORT is the optimal baseline configuration. Two baselines have been used to benchmark the proposal. Both Base-SHORT and Base-LONG simulate an out of order configuration with a full-ported centralized physical register file in the back-end. This architecture is based on the MIPS R10000 microarchitecture [1]. Base-SHORT simulates an architecture with a three-stage front-end and a six-stage back-end. This configuration has a pipeline that is one stage shorter than the FPRF pipeline. The performance will be higher not only because it does not have conflicts in accessing the register file, but also because the branch misprediction penalty is smaller than in the FPRF proposal. This is the reason whye Base-LONG is introduced.

- 2. *Base-LONG* is an architecture identical to Base-SHORT, but with an additional stage in the front-end. This model is identical to the FPRF model in number of cycles paid when a branch misprediction happens.

- 3. *FPRF-8B2R2W* is the FPRF with 8 banks, 2 read ports and 2 write ports each. It matches the configurations that Tseng et al. present in their paper on banked register files [21]. This configuration is the base case without optimizations. The pipeline depth is equal to Base-LONG.

- 4. *FPRF-8B2R2W-RS* is identical to the FPRF-8B2R2W configuration plus read sharing as described in Sect. 3.2.

- 5. *BMRF-OPT* is an optimistic implementation of the banking strategy described in [21]. This proposal needs to speculatively issue instructions to the functional units. If later a conflict occurs when the instruction wants to read its operands, a bubble is inserted in the pipeline for the conflicting instruction while the correct state of

| Configuration  | #Banks | Read Ports<br>per Bank |           | Read Sharing | Bubble? | Pipeline<br>Length |

|----------------|--------|------------------------|-----------|--------------|---------|--------------------|

| Base-SHORT     | 1      | Unlimited              | Unlimited | NO           | -       | 9                  |

| Base-LONG      | 1      | Unlimited              | Unlimited | NO           | -       | 10                 |

| FPRF-8B2R2W    | 8      | 2                      | 2         | NO           | -       | 10                 |

| FPRF-8B2R2W-RS | 8      | 2                      | 2         | YES          | -       | 10                 |

| BMRF-OPT       | 8      | 2                      | 2         | YES          | NO      | 10                 |

| BMRF-STALL     | 8      | 2                      | 2         | YES          | YES     | 10                 |

Table 2. Main differences between configurations

the microarchitecture is recovered. This model is optimistic because it assumes that there is no need to kill the full issue group and that the architecture can recover at once.

6. BMRF-STALL is the same implementation as BMRF-OPT but in this case it takes into account that a full bubble is inserted in the pipeline when a conflict occurs in the access to the register file and thus the full issue group is killed. This configuration approximates the work done in Tseng et al. [21] but, as will be verified later, it is still optimistic because some constraints have been left out of the simulated architecture.

For the evaluation of *writeback filtering* the FPRF-8B2R2W-RS architecture has been used.

## 5 Performance Evaluation

First, the amount of instruction level parallelism in the FPRF architecture is evaluated. On average, the architecture should be slower than both Base-SHORT and Base-LONG, because these architectures never stall and, in the case of Base-SHORT, the pipeline is shorter which makes branch recovery faster for this architecture.

The entire SPEC2000 benchmark suite was simulated for each of the 6 proposed configurations. To ease understanding, only averages and a few selected benchmarks are shown.

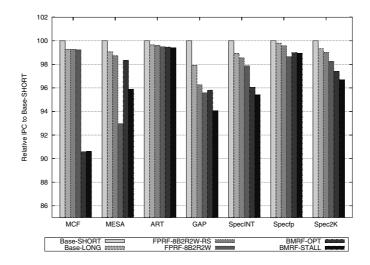

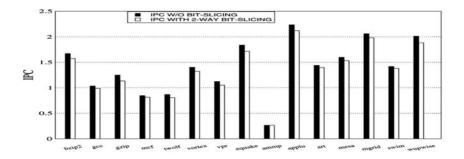

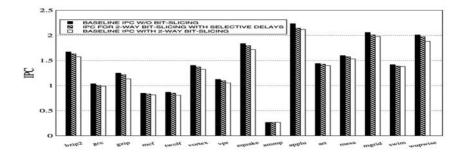

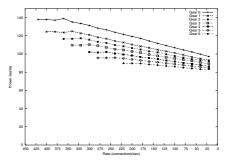

Figure 5 shows the IPC results relative to Base-SHORT. For the full SPEC average (rightmost column) the FPRF architecture, with no optimizations, is only 1.1% worse than Base-LONG. Applying the read sharing optimizations reduces this gap to 0.3%. Both differences are small. However, as can be seen, the behavior shows a lot of variance across benchmarks. For many applications the improvement is far from trivial.

The BMRF-OPT and BMRF-STALL implementations that model the banking strategy described in [21] performed on average 1.9% and 2.7% worse than Base-LONG, respectively. This is because stalls in the back-end have higher impact on performance than stalls in the front-end. These configurations use the read sharing optimization. Compared to our FPRF-8B2R2W-RS implementation, the BMRF implementations lose 1.6% and 2.3% IPC. Our values for the BMRF-STALL implementation are 1.5% better

Fig. 5. Relative IPCs

than the values reported by the original paper. This variation is small and reasonable considering the differences between the modeled architectures: different numbers of physical registers and no operand partitioning between right and left register ports in the simulated BMRF models.

Comparing SpecINT and SpecFP results observes that there is much more IPC loss for integer benchmarks than for floating point programs. There are many reasons for this. For the specific case of Base-SHORT and Base-LONG, the high rate of mispredicted branches in integer applications is the cause for the IPC loss. FP programs have fewer branches and they are more predictable. Other columns of the plot show similar behavior. The reason FP programs have less IPC loss is because many more instructions are in the instruction queues and stalls in the front-end can be easily absorbed by the back-end. In addition , the fact that FP programs perform simultaneous FP and integer calculations helps to reduce the conflicts because both types of instructions access different register files.

Finally, the four selected benchmarks (MCF, MESA, ART and GAP) show how much the performance is dependent on program characteristics. The selected benchmarks show the widest variation observed across all of the SPEC benchmark.

## 5.1 Energy Consumption

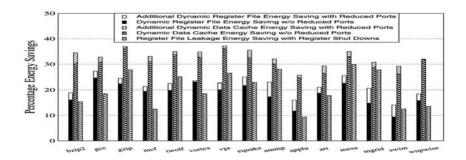

One of the main benefits of implementing banking is to reduce the power consumption of the register file. The banking technique has long been known to reduce energy, but the complexity of control logic and potential loss in IPC, have precluded its use in register files. The banking scheme for the FPRF takes advantage of the reduced access rate to this structure when it is located in the front-end.

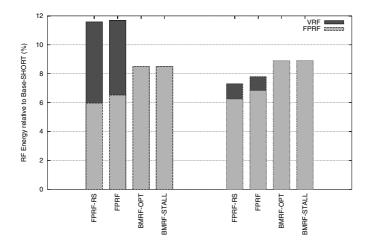

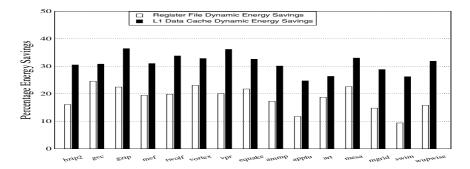

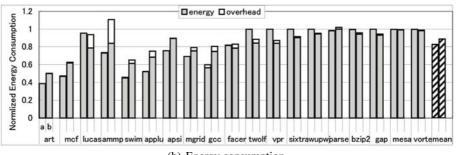

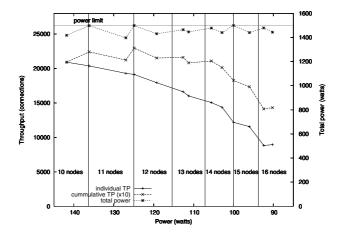

In this section the energy requirements of the register files of the FPRF architecture are evaluated. The energy model for the register file proposed by Rixner et al. [24] is

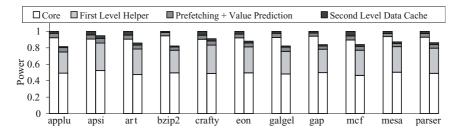

used to obtain the energy of individual Rd/Wr access, which are then multiplied by the number of accesses to the register file. In the results, the values are averaged over all benchmarks of SPEC2000. Only the banked architectures are evaluated here using two different organizations for the instruction queues. The first type of back-end uses a centralized *Value Register File*. This is a heavily multiported structure (4 read ports and 10 write ports are needed). The results for this configuration are shown on the left side of Figure 6 relative to the power consumed by the centralized *Base-SHORT* architecture. The energy is given for both the FPRF and the VRF. The results show that the register distribution and banking techniques effectively reduce the energy consumed. Up to 94% of the Base-SHORT energy can be saved by combining the banked FPRF architecture with read sharing. On the other hand, although the VRF has fewer accesses and only 32 entries, its large number of ports increases the energy consumption compared to [21], which lacks a VRF. A detailed study of the VRF is outside of the scope of this paper.

Fig. 6. Relative energy with a centralized VRF (left) and a distributed VRF (right)

An alternative organization based on multiple queues is also modeled, similar to the POWER4 microprocessor [25]. This microarchitecture uses multiple small instructions queues instead of one large centralized queue. Each queue has smaller issue capabilities (1-way) and less entries, which considerably reduces the number of ports (only 1 read port and 6 write ports, one for every source functional unit, are now required). 4 issue queues of 8 entries for both integer and FP datapaths are used here. The energy of such a distributed scheme is shown on the right side of Figure 6. Using this approach the energy of the VRF is reduced by 82% and the total energy is now 18% below the power consumed by the BMRF model. Using this IQ organization in the BMRF model would have no effect as, like the Power4, this model still requires the presence of a centralized register file that cannot be distributed. The new distributed scheme will have some IPC loss, but this will affect all architectures. A detailed analysis of this technique is outside the scope of this paper.

## 5.2 Writeback Filtering

The energy of the FPRF can be reduced even more by using *writeback filtering*. This technique has no effect on IPC, but it can have an impact on the energy because it reduces the number of writes into the register file. We measured the number of writebacks that can be filtered out from Spec2000 and observed that about 22% of all integer writebacks could be filtered out using this technique. The number of floating point writebacks is somewhat smaller, with 18% of all floating point results being short–lived values, which are candidates for writeback filtering. The energy reduction is expected to be somewhat smaller as only some writes but no reads are removed. For the full SPEC suite, the energy due to accesses to the integer register file is reduced by 12.1%. For SpecFP the energy due to accesses to the floating point register file is reduced by 13%.

These improvements are still limited. The main reason is the way load misses are handled. The need to replay load misses forces to add registers that appear in load rename maps to the rename stack where writeback filtering is analyzed. The number of loads is large and so is the number of additional maps. Not all implementations force loads to replay restarting from architectural state. Some processors use a scheme in which instructions that depend on a load are kept in the instruction queues until the load resolves in case they have to be reissued. This allows the processor to recover directly from the issue queues in case of a load scheduling conflict. In such a scheme less registers will be written back into the FPRF because many checkpoints will be gone. As an alternative, loads can be associated to previous checkpoints taken on branches. In the case of a load replay, the processor will recover from a previous checkpoint and re-execute the load in the correct order. This approach, which is expected to suffer marginal IPC degradation, is reminiscent of the concept of checkpointed commit [26].

In this alternative implementation on the FPRF up to 55% of all integer writebacks and up to 67% of all FP writebacks can be filtered out. These values are much closer to the expected gains. In terms of energy, this means that up to 30% of the energy can be saved in the integer FPRF and up to 47% can be removed from the floating point FPRF. These values may seem very large but it has to be remembered that the FPRF provides only 20-40% of the operands, so the bulk of accesses to this register file are writes. This is what makes the writeback filtering technique so attractive. On the downside, maintaining load-dependent instructions in the queue until the resolution of the load will have a negative impact on IPC because the queues will fill sooner. Therefore the checkpointing approach is prefereable.

The use of *writeback filtering* is interesting because it allows to attack the energy problem from two perspectives. Positioning the physical register file in the front—end allowed to reduce the number of read accesses because many registers don't have computed values at this point. Writeback filtering, on the other hand, reduces the number of writeback accesses. Thus this combination of techniques allows simultaneous reduction in both read and write accesses.

## 6 Conclusions

This paper proposed and analyzed a new register file architecture combining the best of the Future File and the centralized physical register file. This combination reduces RF access frequency and maintains fast misprediction recovery. It was shown that this architecture is well suited for the application of register file banking with read sharing and writeback filtering. Minimal IPC loss was observed when using a banked register file, considerably less compared to a previous proposal where the physical register file is in the back-end [21]. Only 0.3% of IPC was lost due to the banking conflicts, down from 1.6% in the previous proposal.

Writeback Filtering was proposed to reduce the number of writes to the register file. Two possible implementations of this were discussed. The first one used the architectural state to replay loads while the second replayed the loads by associating them with previous checkpointed branches.

The second configuration was able to remove about 60% of all writebacks, while the first only removed about 20%.

## Acknowledgments

This work has been supported by the Ministry of Education of Spain under contract TIN–2004–07739–C02–01, the HiPEAC European Network of Excellence, the CEPBA and the Barcelona Supercomputing Center.

## References

- 1. Yeager, K.C.: The MIPS R10000 superscalar microprocessor. IEEE MICRO 16 (1996) 28–41

- Gonzalez, R., Cristal, A., Pericàs, M., Veidenbaum, A., Valero, M.: Scalable distributed register file. In: Proc. of the 4th Workshop on Complexity-Effective Design (WCED). (2004)

- 3. Levitan, D., Thomas, T., Tu, P.: The PowerPC 620 microprocessor: A high performance superscalar RISC microprocessor. In: Proc. of COMPCON'95. (1995) 285–291

- Zyuban, V., Kogge, P.: The energy complexity of register files. In: Intl. Symp. on Low Energy Electronics and Design. (1998) 305–310

- Seznec, A., Toullec, E., Rochecouste, O.: Register write specialization register read specialization: a path to complexity-effective wide-issue superscalar processors. In: Proc. of the 35th Intl. Symp. on Microarchitecture. (2002) 383–394

- Park, I., Powell, M.D., Vijaykumar, T.: Reducing register ports for higher speed and lower energy. In: Proc. of the 35th Annual Intl. Symposium on Microarchitecture. (2002)

- 7. Kim, N.S., Mudge, T.: Reducing register ports using delayed write-back queues and operand pre-fetch. In: Proc. of the 17th ACM Intl. Conf. on Supercomputing. (2003)

- 8. Gonzalez, R., Cristal, A., Ortega, D., Veidenbaum, A., Valero, M.: A content aware integer register file organisation. In: Proc. of the 31th Intl. Symp. on Computer Architecture. (2004)

- Cruz, J., González, A., Valero, M., Topham, N.: Multiple-banked register file architecture.

In: Proc. of the 27th Intl. Symp. on Computer Architecture. (2000) 316–325

- Balasubramonian, R., Dwarkas, S., Albonesi, D.: Reducing the complexity of the register file in dynamic superscalar processors. In: Proc of the 34th Intl. Symp. on Microarchitecture. (2001)

- Zalamea, J., Llosa, J., Ayguadè, E., Valero, M.: Two-level hierarchical register file organization for VLIW processors. In: Proc of the 33th Intl. Symp. on Microarchitecture (MICRO-33). (2000) 137–146

- 12. Palacharla, S., Jouppi, N., Smith, J.: Complexity-effective superscalar processors. In: Proc. of the 24th Intl. Symp. on Computer Architecture. (1997)

- 13. Moudgill, M., Pingali, K., Vassiliadis, S.: Register renaming and dynamic speculation: an alternative approach. In: Proc. of the 26th. Intl. Symp. on Microarchitecture. (1993) 202–213

- Balasubramonian, R., Dwarkadas, S., Albonesi, D.: Dynamically allocating processor resources between nearby and distant ilp. In: Proc. of the 28th Intl. Symp. on Computer Architecture. (2001) 26–37

- Martinez, J., Renau, J., Huang, M., Prvulovic, M., Torrellas, J.: Cherry: Checkpointed early resource recycling in out-of-order microprocessors. In: Proc. of the 35th Intl. Symp. on Microarchitecture. (2002) 3–14

- 16. González, A., González, J., Valero, M.: Virtual-physical registers. In: Proc of the 4th Intl. Symp. on High-Performance Computer Architecture. (1998)

- 17. Lipasti, M.H., Mestan, B., Gunadi, E.: Physical register inlining. In: Proc. of the 31th Intl. Symp. on Computer Architecture. (2004)

- 18. Balakrishnan, S., Sohi, G.: Exploiting value locality in physical register files. In: Proc. of the 36th Intl. Symp. on Microarchitecture. (2003)

- 19. Smith, J.E., Pleszkun, A.R.: Implementation of precise interrupts in pipelined processors. Proc. of the 12th Intl. Symp. on Computer Architecture (1985) 34–44

- Keltcher, C., McGrath, K., Ahmed, A., Conway, P.: The amd opteron processor for multiprocessor servers. IEEE MICRO 23 (2003) 66–76

- Tseng, J., Asanovic, K.: Banked multiported register files for high-frequency superscalar microprocessors. In: Proc. of the 30th Annual Intl. Symp. on Computer Architecture. (2003)

- 22. Ponomarev, D., Kucuk, G., Ergin, O., Ghose, K.: Reducing datapath energy through the isolation of short-leved operands. In: Proc. of the 12th Intl. Conf on Parallel Architectures and Compiler Techniques. (2003)

- 23. Sami, M., Sciuto, D., Silvano, C., Zaccaria, V., Zafalon, R.: Exploiting data forwarding to reduce the power budget of vliw embedded processors. In: Proc. of the Conference on Design, automation and test in Europe. (2001) 252–257

- Rixner, S., Dally, W.J., Khailany, B., Mattson, P.R., Kapasi, U.J., Owens, J.D.: Register organization for media processing. In: Proc. of the 6th Intl. Symp. on High Performance Computer Architecture. (2000) 375–386

- 25. Tendler, J., Dodson, S., Fields, S., H. Le, B.S.: Power4 system microarchitecture. IBM Journal of Research and Development 46 (2002)

- 26. Cristal, A., Valero, M., Gonzalez, A., LLosa, J.: Large virtual ROBs by processor check-pointing. Technical report (2002) Technical Report number UPC-DAC-2002-39.

## Reducing Delay and Power Consumption of the Wakeup Logic Through Instruction Packing and Tag Memoization

Joseph Sharkey<sup>1</sup>, Dmitry Ponomarev<sup>1</sup>, Kanad Ghose<sup>1</sup>, and Oguz Ergin<sup>2</sup>

Department of Computer Science, State University of New York, Binghamton, NY 13902-6000 {jsharke, dima, ghose}@cs.binghamton.edu Intel Barcelona Research Center, Intel Labs, UPC, Barcelona, Spain Oquzx.ergin@intel.com

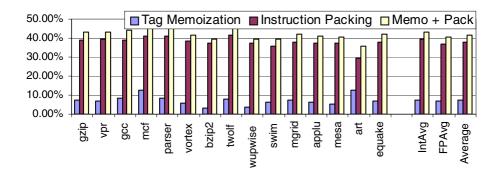

Abstract. Dynamic instruction scheduling logic is one of the most critical components of modern superscalar microprocessors, both from the delay and power dissipation standpoints. The delay and energy requirement of driving the result tags across the associatively-addressed issue queue accounts for a significant percentage of the scheduler's overhead and also limits the design scalability. We propose two schemes to reduce the power consumption and the delays of the wakeup logic. Our first scheme – instruction packing – shares the associative part of an issue queue entry between two instructions, each with at most one non-ready source. As a result, the number of entries in the issue queue (and, hence, the length of the tag buses) can be reduced by a factor of two with almost no impact on the IPCs, because most instructions either enter the pipeline with at least one of their source operands ready, or do not make use of two source registers to begin with. Our second scheme - tag memoization avoids driving the upper portion of the tags, if those bits did not change their values from what was driven on the same tag bus during the most recent broadcast. While instruction packing results in the reduced length of the tag buses, tag memoization reduced the number of tag lines that need to be driven. We evaluate our designs using detailed microarchitectural simulations of the SPEC 2000 benchmarks and the SPICE simulations of the issue queue layouts.

## 1 Introduction

Modern superscalar processors use out of order execution to exploit instruction level parallelism. The dynamic scheduling engine employed in such processors often uses associative logic embedded into the issue queue entries to wakeup instructions that are awaiting a result. This is accomplished by storing the address of the source registers within the issue queue entries and using the comparators that match the stored source register values against the address of the result that is driven on tag bus lines. A significant amount of energy dissipation results as the destination register address is driven on the tag busses. Energy dissipation occurs when the tag bus lines

are driven because of the charging and discharging of the wire capacitance of the tag line itself and the gate capacitance of the devices that implement the tag comparators. As wire capacitances dominate, a significant fraction of the energy spent in waking up instructions is attributed to the power used for driving the tag busses. This is particularly true if comparators that dissipate energy only on a match are used within the issue queue [27].

The scope of this paper is to propose two fairly orthogonal techniques for reducing the energy dissipated in driving the tag lines. Our first approach reduces the effective length of the tag bus lines and the number of comparator bits driven by essentially reducing the number of issue queue entries through the opportunistic packing of two instructions into a single issue queue entry. Our second approach avoids the power dissipated in driving the tag lines by not driving the higher order bits in the tag bus if their value matches the corresponding values last driven on the same tag bus. We validate the power savings achieved by using our techniques through the cycleaccurate simulations of SPEC 2000 benchmarks and the circuit simulations of the full-custom issue queue layouts.

## 2 Instruction Packing

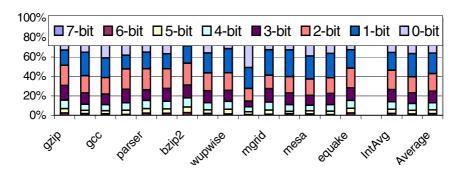

In a traditional RISC-like processor where each instruction can have at most two register source operands, each issue queue (IQ) entry has two comparators, which allow the instruction to track the arrival of both sources by monitoring the tag buses. In general, however, such a design results is a grossly inefficient usage of the CAM logic, because of two reasons: 1) Many instructions have only one source register operand, and therefore do not require the use of two tags (and two comparators) in the first place, and 2) of the instructions with 2 source operands, a large percentage have at least one of the source operands ready at the time of dispatch, again rendering the second comparator unnecessary. Our simulations showed that on the average across SPEC 2000 benchmarks, about 83% of the dynamic instructions enter the scheduling window with at least one of their source operands ready.

Fig. 1. Traditional IQ entry format

These statistics have been presented before [4] and researchers have proposed different solutions to optimize the IQ design based on this inefficiency. In [4], the non-uniform IQ entry formats were used, i.e. some entries have a full set of tag comparators, other entries have just one comparator, and yet other IQ entries have no

comparators. In [28], the tag buses were subdivided into the slow buses and fast buses, such that the tag broadcast on the slow bus is delayed by one cycle. In this paper, we propose a different approach to optimizing the use of the CAM logic within the issue queue by packing multiple (two, for this paper) instructions into the same issue queue entry, effectively duplicating the RAM storage for these instructions (destination register addresses, literals, opcodes) and sharing the existing CAM logic. In effect, the aspect ratio of the issue queue changes: the number of issue queue entries become lower and the width of each entry goes up. In this section, we describe the details of our design.

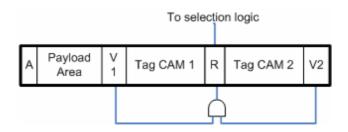

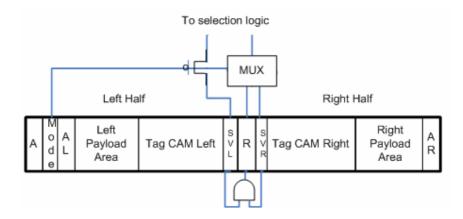

Figure 1 shows a format of the issue queue entry used in traditional designs. The following fields comprise a single entry: a) entry allocated bit (A), b) payload area (opcode, FU type, destination register address, literals), c) tag of the first source, associated comparator (tag CAM word 1, hereafter just tag CAM 1, without the "word") and the source valid bit, d) tag of the second source, associated comparator (tag CAM 2) and source valid bit, and e) the ready bit. The ready bit, used to raise the request signal for the selection logic is set by AND-ing the valid bits of the two sources.

If at least one of the source operands is ready at the time of dispatch, the tag CAM associated with this instruction's IQ entry remains unused. To exploit this idle tag CAM, we propose to share one issue queue entry between two such instructions. An entry in the IQ can now hold one or two instructions, depending on the number of ready operands of the stored instructions at the time of dispatching. Specifically, if both source registers of an instruction are not available at the time of dispatch, the instruction is assigned an IQ entry of its own and makes use of both tag CAMs in the assigned entry to determine when its operands are ready. An instruction that has only one source register that is not available at the time of dispatch is assigned just one half of an IQ entry. The remaining half of the IQ entry may be used by another instruction that also has one of its source registers unavailable at the time of dispatch. Sharing an IQ entry between two instruction also requires the IQ entry to be widened to permit the payload parts of both instructions to be stored, along with the addition of flags that indicate whether the entry is shared between two instructions and the status of the stored instruction(s). Figure 2 shows the format of an issue queue entry that supports instruction packing. Each IQ entry is comprised of the "entry allocated" bit (A), the ready bit (R), the mode bit (MODE) and the two symmetrical halves: the left half and the right half. The structure of each half is identical, so we will use the left half for the subsequent explanations.

A left half of each IQ entry contains the following fields:

- 1. Left half allocated (AL) bit. This bit is set when the half-entry is allocated.

- Source tag and associated comparator (Tag CAM). This is where the tag of the non-ready source operand for an instruction with at most one non-ready source is stored.

- 3. Source valid left bit (SVL). This bit signifies the validity of the source from part b), similar to traditional designs. This bit is also used to indicate if the instruction residing in a half-entry is ready for selection (as explained later)

- 4. Payload area. The payload area contains the same information as in the traditional design, namely: opcode, bits identifying the FU type, destination register address and literal bits. In addition, the payload area contains the tag of the second source.

Notice that the tag of the second source does not participate in the wakeup, because if an instruction is allocated to a half-entry, the second source must be valid at the time of dispatch. Compared to the traditional design, the payload area is increased by the number of bits used to represent a source tag.

The contents of the right half are similar. The ready bit (R) is used when an instruction with two non-ready source operands is allocated into the full IQ entry, as explained below. To summarize, each entry in the modified IQ is divided into a left half and a right half, each is capable of storing an instruction with at most one non-ready source operand, or the two halves can be used in concert to house an instruction with 2 non-ready source operands. In general, the issue queue entry can be in one of the following three states: 1) the entry holds a single instruction, both source operands of which were not ready at the time of dispatch, 2) the entry holds two (or one with another half free) instructions, each of which had at least one source operand ready at the time of dispatch, or 3) the entry is free. The "mode" bit, stored within each IQ entry as shown in Figure 2, identifies the state of the entry. If the mode bit is set to 1, then the entry maintains a 2-operand instruction, otherwise it either maintains one or two single-operand instructions or it is free.

Since each entry can hold up to two instructions, fewer IQ entries are needed. However, despite the fact that each entry in the modified IQ shown in Figure 2 is somewhat wider than the traditional queue entry (due to the replication of the Payload area and three extra bits – AL, AR, and MODE), the amount of CAM logic per-entry does not change. Each entry still uses only two comparators – those are either used by one instruction, which occupies full entry, or are shared by two instructions, each located in half-entry. In the next few subsections, we describe the details of this technique.

Fig. 2. Wakeup and Selection Logic Modified to Support Instruction Packing

## 2.1 Entry Allocation

To set up an issue queue entry for an instruction, the entry allocated bits corresponding to both halves (AL and AR), as well as the global "entry\_allocated" bit

(A) are associatively searched in parallel with register renaming and checking the status of source physical registers. If the instruction is determined to have at most one non-ready source operand, the lowest numbered issue queue entry with at least one available half is allocated. If both halves are available within the chosen entry, then the instruction is written into the right half. After the appropriate half is chosen, both the "entry\_allocated" bit of this half and the global A bits are reset. If an instruction is determined to have 2 non-ready source operands, then a full-sized entry is allocated, as dictated by the state of the A bits. The search for a full-sized and a half-sized entry occurs simultaneously, and the entry to be allocated is then chosen based on the number of non-ready source operands. This IQ entry allocation process is somewhat more complicated than similar allocation used in traditional designs, where just the A bits are associatively searched. However, there is no extra delay involved, because the searches occur in parallel. Similar issues with allocating the IQ entries are also inherent in other designs which aim to reduce the amount of associative logic in the queue by placing the instructions into the issue queue entries judiciously, based on the number of non-ready operands at the time of dispatch [4]. We will discuss what kind of information is written into the IQ for the various instruction categories later in the paper. But first, we describe how wakeup and selection are implemented in this scheme.

## 2.2 Instruction Wakeup

The process of instruction wakeup remains exactly the same as in traditional design for an instruction that occupies a full IQ entry (i.e. comes with 2 non-ready sources). Here, the ready bit (R) is set by AND-ing the valid bits of both sources. For instructions which occupy half of an IQ entry, the wakeup simply amounts to setting of the valid bit corresponding to the source that was non-ready when the instruction entered the IQ. The contents of the source valid bits are then directly used to indicate that the instruction is ready for selection (the validity of the second source is implicit in this case). The selection logic details are described next.

#### 2.3 Instruction Selection

The process of instruction selection needs to be slightly modified to support instruction packing. To make the explanation easier, we assume that a 32-entry IQ is packed into a 16-entry structure, such that each entry is capable of holding two instructions with at most one non-ready source each, or one instruction with two non-ready sources. In a 32-entry IQ design, there are 32 request lines that can be raised by the awakened instructions – one line per IQ entry. In the instruction packing scheme, each of the two halves of each of the 16 entries requires a request line, thus retaining the same total number of request lines (32) and resulting in a similar complexity of the selection logic. In addition, the ready bits, used by the instructions allocated to full entries, also require request lines. Consequently, a straightforward implementation of the selection logic would require 48 (3x16) request lines, thus increasing the complexity, delay and power requirements of the select mechanism.

Such an undesirable elevation in the complexity of the selection logic can be avoided by sharing one request line between the R and the SVR bits. The shared

request line is raised if at least one of the bits (the R or the SVR) is set. The R and the SVR bits are both connected to the shared request line through a multiplexor, which is controlled by the "mode" bit of the IQ entry (Figure 2). Consequently, the overall delay of the selection logic increases only slightly – by the delay of a multiplexor. Notice also that the MUX control signal (the "mode" bit) is available in the beginning of the cycle when the selection process takes place (the "mode" bit is set when the issue queue entry is allocated). The request line driven by the SVL bit is controlled by the p-device, whose gate is connected to the "mode" bit. This request line will be asserted only if the "mode" bit is set to 0 (indicating that the IQ entry is shared between two instructions) and the SVL bit is set to 1.

Note that the only part of the selection logic that is modified is the process of asserting the request lines. The rest of the selection logic is unchanged compared to the traditional designs. The overall delay of the selection logic is thus increased by the delay of the multiplexor, whose control signal is preset (as the value of the "mode" bit is available as soon as the IQ entry is allocated).

#### 2.4 Instruction Issue

We define instruction issue as a process of reading the source operand tags of the selected instructions and starting the register file access (effectively moving the instruction out of the IQ). When a grant signal comes back corresponding to the request line, which was shared between the R and the SVR, the issue logic has to know which physical registers have to be read. Conventionally, this information is conveyed by the contents of the tag fields. However, the register tags of an instruction with two non-ready sources (i.e. the instruction that occupies full IQ entry) and the register tags of an instruction with one non-ready source are generally stored in different locations within the IQ entry. In the former case, the tags are stored in the tag fields connected to both comparators – one tag is stored in the left half of the entry and the other tag is stored in the right half of the entry, such that the tag of the non-ready operand is connected to the comparator and the other tag is simply stored in the payload area. Given this disparate locations of the source register tags, how would the issue logic know which tags to use when the grant signal corresponding to a shared request line comes back?

One solution is, again, to use the contents of the "mode" bit and a few multiplexors. This will, however, slightly increase the delay of the issue / register access cycle. A better solution, which avoids the additional delays in instruction issuing altogether, is as follows. When an instruction with two non-ready sources is allocated to the issue queue, the tag, which is connected to the left half comparator, is also replicated in the payload area storage for the second tag in the right half. As a result, both tags will be present in the right half of the queue, so these tags can be simply used for register file access, without regard for the IQ entry mode.

## 2.5 Benefits of Instruction Packing

Instruction packing, as described in this section, has several benefits over the traditional issue queue designs in terms of layout area, access delays and power consumption.

The area of the issue queue decreases, because compared to the traditional designs, the amount of RAM storage does not change (we use twice as fewer entries, but each entry has about twice the amount of RAM), but the amount of associative logic is reduced by a factor of two.

The delay of the wakeup logic is reduced, because the tag buses become much shorter and the capacitive loading on these buses is also significantly reduced – the delay in driving the tag bus (which is a major component of the wakeup latency) is roughly reduced by half. Furthermore, shorter bitlines can potentially reduce the IQ access delays during instruction dispatching (setting up the entries) and issuing (reading out the register tags and literals). Finally, for the same reasons the power consumption is also reduced. Another potential reason for the reduction in the power consumption has to do with the use of fewer comparators. In the instruction packing, the tags of the source registers ready during dispatching are never associated with the comparators. In the traditional designs, each and every source tag is hooked up to a comparator. Unless these comparators are precharged selectively (based on whether or not a given IQ slot is awaiting for the result), unnecessary dissipations can occur than comparators associated with the already valid sources continue to fire.

In the result section, we quantify these savings using detailed simulations of SPEC 2000 benchmarks and also circuit simulations of the IQ layouts. Notice that all these benefits are achieved with essentially no degradation in the IPCs (committed Instructions Per Cycle). This is because most instructions (our results show 83%) have at least one of their sources ready at the time of dispatch, thus rendering the performance loss due to the smaller number of IQ entries negligible.

## 3 Tag Memoization

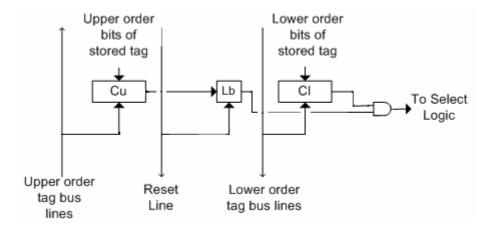

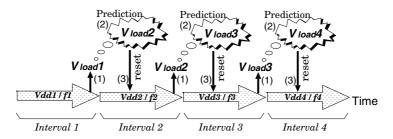

The tag memoization scheme exploits the fact that the higher-order bits of the tags that are broadcasted within a short duration of each other are likely to be the same. The idea here is to conserve power expended in driving the tag by not driving the higher-order tag bits if they happen to match the higher-order tag bits that were driven on the same bus during the previous broadcast. The tag comparator used to match the tag on the bus is broken into two separate comparators, say Cu and Cl, to match the higher-order bits and the remaining lower-order bits, respectively. A 1-bit latch is inserted in between to remember if there was a match in the higher order bits with the previous broadcast. The match signal for an entry is derived by AND-ing the output of this latch with the output of the comparator for the lower order bits. Figure 3 depicts this logic. We now describe this scheme in some detail.

Let Lb designate the latch used within an IQ entry to remember the match with the upper order bits driven on bus b with the tag value stored within a register operand field of the IQ entry. The tag driver logic for tag bus b also uses a latch array, Ub, to remember the upper order bits of the tag pattern that was driven onto the tag bus b. The following two cases arise when a tag value is to be driven on a tag bus:

If the upper bits driven on the bus b in the next broadcast match Ub, then only the lower order bits are driven on the tag bus. Entries that match the lower order bits and have their latch Lb set now produce a match signal. If, however, the upper order bits

driven on the bus b do not match the contents of Ub, then the following actions are taken concurrently:

- The reset line shown in Figure 3 is driven to clear the contents of latch Lb in all of the IQ entries.

- Both upper and lower order bits of the tag are driven out on bus b.

- Ub is updated.

Clearing Lb in this case allows each entry to produce a match based on all of the tag bits - both upper order and lower-order bits.

The tag memoization scheme saves power by not driving the upper order bits of a tag bus whenever possible. The power savings are somewhat defeated by the need to drive the reset line on each tag bus, by the need to maintain the Ub latch, and dissipations within the Lb and the AND-gate used within each entry. One can save additional power dissipation by using the contents of Lb to disable Cu once Lb is set. Doing so prevents Cu from dissipating any power from false matches with the values floating on the upper order bits of the bus.

From a delay standpoint, the AND-ing of Lb with the output of Cl adds a slight delay in the generation of a request signal from matching entries. This added delay is however compensated to some extent by the smaller delay of Cl. (Cl has a smaller response time compared to that of a comparator that compares all bits of the tag value.)

Fig. 3. Tag comparator configuration for the tag memoization scheme

One can force additional savings from the memoization scheme by assigning tag broadcasts to a bus whose Ub matches the upper order bits of the tag value to be driven. We call this "intelligent" tag bus assignment. There is, of course, some energy overhead in assigning tag broadcasts to specific buses in this case. Another possibility, and one that we have not explored here, is to assign the tag values sequentially to instructions. This is possible in datapaths that use the ROB slots as physical registers or have rename buffers that are assigned from a circular FIFO. In

this paper, we only considered a datapath with the unified physical/architectural register file, where the allocation of physical registers can occur from anywhere within the register file, as dictated by the free list.

The approach just described can be generalized to accommodate the segmentation of the tag comparator into more than two parts requiring an intervening latch in between consecutive segments. For example, an 7 bit tag comparator can be segmented into three parts: Ca(upper order two bits), Cb(next two bits), and Cr (remaining 3 bits). This arrangement requires two latches: one between Ca and Cb and another between Cb and Cr; there is a reset line for each latch. These latches may be set independently, allowing for the gating off of either set of bits, or both. The match signal is derived by AND-ing the contents of the intervening latches and the output of the comparator segment covering the lower order bits.

| Parameter                                | Configuration                                                                                                                   |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Machine width                            | 4-wide fetch, 4-wide issue, 4 wide commit                                                                                       |

| Window size                              | Issue queue: as specified,48 entry load/store queue, 96-entry ROB                                                               |

| Function Units and Latency (total/issue) | 4 Int Add (1/1), 2 Int Mult (3/1) / Div (20/19), 2 Load/Store (2/1), 2 FP Add (2), 2 FP Mult (4/1) / Div (12/12) / Sqrt (24/24) |

| Physical Registers                       | 128 combined integer + floating-point physical registers                                                                        |

| L1 I-cache                               | 64 KB, 1-way set-associative, 128 byte line, 1 cycles hit time                                                                  |

| L1 D-cache                               | 64 KB, 4-way set-associative, 64 byte line, 2 cycles hit time                                                                   |

| L2 Cache unified                         | 2 MB, 8-way set-associative, 128 byte line, 6 cycles hit time                                                                   |

| ВТВ                                      | 2048 entry, 2-way set-associative                                                                                               |

| Branch Predictor                         | Combined with 1K entry Gshare, 10 bit global history, 4K entry bimodal, 1K selector                                             |

| Branch Mispred. Penalty                  | 8 cycles minimum                                                                                                                |

| Memory                                   | 128 bit wide, 150 cycles first chunk, 1 cycles interchunk                                                                       |

| TLB                                      | 32 entry (I), 128 entry (D), fully associative, 12 cycles miss latency                                                          |

Table 1. Configuration of the simulated processor

## 4 Simulation Methodology

Our simulation environment includes a detailed cycle accurate simulator of the microarchitecture and cache hierarchy. While our simulator was developed from scratch, it uses the same binaries, system call interface and tools as the MIPS-like Simplescalar PISA ISA. All benchmarks were compiled with gcc 2.6.3 (compiler options: -O2) and linked with glibc 1.09, compiled with the same options. All simulations were run on a subset of the SPEC 2000 benchmarks consisting of 8 integer and 7 floating-point benchmarks. In all cases, predictors and caches were warmed up for 1 billion committed instructions and statistics were gathered for the next 200 million instructions. Table 1 presents the configuration of the baseline processor.

For estimating the delay, energy and area requirements, we deigned the actual VLSI layouts of the issue queue and simulated them using SPICE. The layouts were designed in a 0.18 micron 6 metal layer CMOS process (TSMC) using Cadence design tools. A Vdd of 1.8 volts was assumed for all the measurements.

#### 5 Results

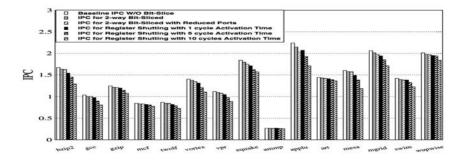

## 5.1 Instruction Packing

Table 2 shows the IPC loss due to instruction packing. These results are displayed in the form of a table rather than a graph because IPC differences are too small to be noticeable on the traditional bar graph. The columns, in order, show IPC results with a 32-entry issue queue, a 16-entry issue queue with instruction packing, an 8-entry IQ, and a 4-entry IQ with packing. The results show that a 16-entry issue queue utilizing instruction packing performs within 0.5% of a traditional 32-entry IQ. The configuration with an 8-entry queue packed into 4 wider entries is only shown to demonstrate that packing does not significantly degrade the performance even for very small issue queues. Here, for example, the performance loss is only 5.3% on the average.

**Table 2.** IPC for 32 and 8-entry traditional queues as compared to 16 and 4-entry queues supporting instruction packing

| Benchmarks | 32IQ  | 16IQ_PACK | 8IQ   | 4IQ_PACK |

|------------|-------|-----------|-------|----------|

| Gzip       | 1.544 | 1.587     | 1.594 | 1.412    |

| Vpr        | 1.463 | 1.447     | 1.279 | 1.125    |

| Gcc        | 1.128 | 1.128     | 1.105 | 1.032    |

| Mcf        | 0.444 | 0.442     | 0.398 | 0.343    |

| Parser     | 1.317 | 1.304     | 1.234 | 1.118    |

| Vortex     | 1.996 | 2.001     | 1.908 | 1.672    |

| bzip2      | 1.594 | 1.546     | 1.480 | 1.272    |

| Twolf      | 1.209 | 1.161     | 1.104 | 0.968    |

| Wupwise    | 2.212 | 2.212     | 1.924 | 2.212    |

| Swim       | 1.511 | 1.511     | 1.412 | 1.269    |

| Mgrid      | 1.218 | 1.218     | 1.210 | 1.218    |

| Applu      | 1.337 | 1.337     | 1.345 | 1.278    |